32位RISC微处理器的模块化设计

VIP免费

摘 要

嵌入式微处理器以其高性能、低功耗、便携式的优点,越来越广泛的应用于

各种电子设备中。其中 R1SC(Reduced Instruction Set Computer),即精简指令集

计算机,作为计算机设计策略的一种类型己越来越多地应用于计算机的体系设

计中。论文在对嵌入式微处理器通用结构研究的基础上,参考精简指令系统,实

现了微处理器的基本结构。本文所设计的微处理器采用五级流水线结构,分别为

取指令(instruction Fetch) 级、指令译码(Instruction Decode) 级、指令执行

(Execution)级、存储器访问(Memory access)级和回写(Write Back)级。论文阐述了

流水线设计过程,并对流水线的结构相关问题进行了分析。在具体的电路设计中

采用了自顶向下的方法对处理器进行模块化的划分,整个处理器被划分为许多

个较小的功能模块,这样划分的目的是为了减小设计的复杂程度。数字逻辑设计

采用 Verilog HDL(Verilog 硬件描述语言)进行,首先写出数字逻辑电路的行为级

描述,然后利用仿真软件对所写的行为级描述做功能仿真,并使用综合工具得

到RTL 级网表和门级网表。最后提出了两点改进:(1)采用低功耗数据通路。

(2)为降低芯片面积,将资源共享这一方法应用于设计中。

关键词:精简指令集微处理器,流水线,硬件描述语言,功能验证

I

Abstract

Embedded microprocessor has been applied widely to many kinds of electronic

equipments for its advantage,such as,high performance,lower power cost and portable

characteristic .Especially,as a strategy,Reduced Instruction Set Computer(RISC) is

becoming more popular in the designing of computer architecture.In this paper a basic

architecture of microprocessor is implemented on the base of microprocessor general

architecture and reduced instruction system ,the microprocessor designed above has

five-satgepipeline,including instruction fetch,instruction decode,execution,memory

access and write back.The method in designing pipeline and structure hazard were

described in the paper.The design method for the microprocessor is top-down

method,that means the microprocessor is divided into some small functional modules

on the top level.This division will reduce the complexity of design

work.Verilog(Hardware Description Language) is used to describe the digital

logic.The behavioral description of the digital logic circuit is made in Verilog at

first,then this description is functionally simulated by the logic simulation

software,also gained RTL Netlist and gate Netlist with synthesis tool.At last,two

betterment were advanced:(1)Using low-power data path.(2)To decrease the area of

the chip,resource sharing was used in the project.

KEYWORDS:RISC microprocessor,pipeline,HDL,functional verification

II

目 录

第一章 绪论..................................................................................................................1

1.1 课题提出的背景和意义..................................................................................1

1.2 RISC 处理器概述............................................................................................2

1.3 RISC 处理器的发展趋势................................................................................3

1.4 论文主要研究内容及结构安排......................................................................5

第二章 RISC 处理器和其指令系统............................................................................6

2.1 处理器简介.......................................................................................................6

2.2 RISC 处理器的概念和特点............................................................................6

2.2.1 RISC 处理器的概念...............................................................................6

2.2.2 RISC 处理器的特点..............................................................................7

2.3 指令系统..........................................................................................................9

2.3.1 指令系统概述.........................................................................................9

2.3.2 RISC 指令的分类................................................................................11

第三章 HDL 描述与 FPGA 设计...............................................................................14

3.1 HDL 设计简介...............................................................................................14

3.1.1 HDL 设计方法及优点.........................................................................14

3.1.2 HDL 的主要特征.................................................................................15

3.1.3 硬件描述语言的新发展......................................................................16

3.1.4 HDL 设计流程.....................................................................................17

3.2 FPGA 概述.....................................................................................................18

3.3 FPGA 设计方法和流程.................................................................................22

3.3.1 TOP-DOWN 设计方法........................................................................22

3.3.2 FPGA 设计流程...................................................................................23

第四章 RISC 处理器的体系结构...............................................................................28

4.1 流水线结构概述............................................................................................28

4.1.1 流水线操作的概念..............................................................................28

4.1.2 指令流水线的性能..............................................................................28

4.1.3 流水线结构的数据通路......................................................................30

4.1.4 流水线结构相关问题及解决..............................................................32

4.1.5 流水线转移相关问题及解决..............................................................33

4.2 取指令级 IF 设计...........................................................................................34

4.2.1 IF 级的实现结构..................................................................................34

4.2.2 MPC 的替换策略.................................................................................35

4.2.3 BTC 的工作过程.................................................................................35

4.2.4 MPC 和BTC 在流水线中的协同.......................................................36

4.3 指令译码级 ID 设计......................................................................................36

4.3.1 ID 级的实现结构.................................................................................36

4.3.2 ALU 指令译码.....................................................................................38

III

4.3.3 LD/ST 指令译码..................................................................................38

4.3.4 CTR 指令译码.....................................................................................39

4.4 执行级 EXE 设计..........................................................................................39

4.4.1 EXE 级的实现结构.............................................................................39

4.4.2 算术逻辑单元 ALU 的实现................................................................40

4.5 存储器访问级 MEM 设计.............................................................................45

4.6 回写级 WB 设计............................................................................................46

4.7 流水线各级模块任务总结............................................................................47

第五章 功能仿真与综合............................................................................................49

5.1 模块的功能仿真............................................................................................49

5.1.1 功能仿真环境......................................................................................49

5.1.2 功能仿真结果......................................................................................50

5.2 ALU 模块的综合...........................................................................................52

5.2.1 综合工具简介......................................................................................53

5.2.2 ALU 的综合结果.................................................................................53

第六章 RISC 处理器的性能改进..............................................................................58

6.1 低功耗的改进................................................................................................58

6.1.1 低功耗的数据通路结构......................................................................59

6.1.2 低功耗设计的理论计算......................................................................60

6.2 ALU 设计的改进...........................................................................................61

6.2.1 基于资源共享的设计..........................................................................61

6.2.2 传统的 ALU 设计方法........................................................................62

6.2.3 资源共享的 ALU 设计方法................................................................63

6.2.4 等价变换原则......................................................................................65

第七章 总结................................................................................................................67

致 谢............................................................................................................................68

参考文献......................................................................................................................69

研究生期间发表的科技论文......................................................................................72

IV

第一章 绪论

1.1 课题提出的背景和意义

随着大规模集成电路技术日益成熟,微处理器的应用越来越广泛。目前,国

际上微处理器按应用领域的不同可分为三类:一是通用高性能微处理器,主要

应用于工作站和高性能个人计算机系统;二是嵌入式微处理器,主要用于运行

面向特定领域的专用程序,配备轻量级操作系统,比如手机、VCD、机顶盒;三

是微控制器,主要用于汽车空调、自动机械等领域的自控设备。

作为嵌入式系统的核心,嵌入式 CPU 已广泛应用在信息技术的各个领域。

无论是家电产品,多媒体和数字信号处理领域,还是卫星发射、导弹制导、都离

不开微处理器。目前市场上简单的智能电子产品,如全自动洗衣机、电饭煲等,

其内部使用的中央处理器 CPU 相对来说比较简单,一般的8位单片机(如

MCS51,AVR)等,就完全能够胜任。但随着无线通信,多媒体和国际互联网

的发展,各种电子产品趋于微型化,数据处理量越来越大,并且一机多用正在

成为一种潮流。市场上已经出现了 WinCE 可上网手机等典型的高技术产品,在

这些产品中高性能的 CPU 是不可缺的。

展望21 世纪的前50 年,微电子技术对我们既是一个重大的机遇,也是一

个严峻的挑战。随着“后PC 时代”到来,数字化产品层出不穷,嵌入式微处理

器以其低功耗、高性能的特点成为市场新宠。由于嵌入式微处理器还处于起步阶

段,市场潜力巨大,而且没有形成垄断,如果我们能够抓住这个机遇,立足创

新,则有可能使我国微电子技术实现腾飞,在新一代微电子技术中拥有自己的

知识产权,促进我国微电子产业的发展。

RISC(精简指令集计算机)是嵌入式处理器家族中的重要成员,世界各大

半导体厂商都先后推出了 RISC 内核的微处理器。由于其执行速度快,处理能力

强,几乎所有的UNIX 工作站和服务器厂商都采用 RISC 结构的 CPU,所以,

RISC 结构的处理器必将成为未来的主流发展趋势。由此可见,对 RISC 结构处理

器的研究和讨论有着重要的现实意义。

1

摘要:

展开>>

收起<<

摘要嵌入式微处理器以其高性能、低功耗、便携式的优点,越来越广泛的应用于各种电子设备中。其中R1SC(ReducedInstructionSetComputer),即精简指令集计算机,作为计算机设计策略的一种类型己越来越多地应用于计算机的体系设计中。论文在对嵌入式微处理器通用结构研究的基础上,参考精简指令系统,实现了微处理器的基本结构。本文所设计的微处理器采用五级流水线结构,分别为取指令(instructionFetch)级、指令译码(InstructionDecode)级、指令执行(Execution)级、存储器访问(Memoryaccess)级和回写(WriteBack)级。论文阐述了流水线...

相关推荐

-

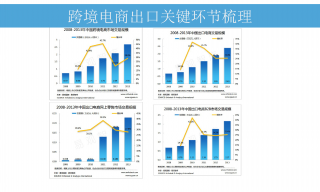

跨境电商商业计划书模版VIP免费

2025-01-09 9

2025-01-09 9 -

跨境电商方案范文VIP免费

2025-01-09 6

2025-01-09 6 -

创业计划书VIP免费

2025-01-09 6

2025-01-09 6 -

xx生鲜APP计划书VIP免费

2025-01-09 6

2025-01-09 6 -

跨境电商创业园商业计划书(盈利模式)VIP免费

2025-01-09 6

2025-01-09 6 -

跨境电商计划书VIP免费

2025-01-09 9

2025-01-09 9 -

绿色食品电商平台项目计划书VIP免费

2025-01-09 8

2025-01-09 8 -

农产品电子商务商业计划书VIP免费

2025-01-09 7

2025-01-09 7 -

农村电商平台商业计划书VIP免费

2025-01-09 8

2025-01-09 8 -

生鲜商城平台商业计划书VIP免费

2025-01-09 7

2025-01-09 7

作者:朱铭铭

分类:高等教育资料

价格:150积分

属性:77 页

大小:8.71MB

格式:DOC

时间:2024-09-20